#### In-Class Homework for Module 1 – No. 1 Wednesday, January 15, 2014

### Given the truth table, below, determine the following:

| X | Y | $\mathbf{Z}$ | F(X,Y,Z) |

|---|---|--------------|----------|

| 0 | 0 | 0            | 1        |

| 0 | 0 | 1            | 1        |

| 0 | 1 | 0            | 0        |

| 0 | 1 | 1            | 1        |

| 1 | 0 | 0            | 1        |

| 1 | 0 | 1            | 0        |

| 1 | 1 | 0            | 0        |

| 1 | 1 | 1            | 1        |

## Truth tables for the dual $F^D(X,Y,Z)$ and complement F'(X,Y,Z) functions:

| X | Y | $\mathbf{Z}$ | $F^{D}(X,Y,Z)$ |

|---|---|--------------|----------------|

| 0 | 0 | 0            |                |

| 0 | 0 | 1            |                |

| 0 | 1 | 0            |                |

| 0 | 1 | 1            |                |

| 1 | 0 | 0            |                |

| 1 | 0 | 1            |                |

| 1 | 1 | 0            |                |

| 1 | 1 | 1            |                |

| <b>3</b> 7 | <b>T</b> 7 | 7 | T3 (T1 T1 D) |

|------------|------------|---|--------------|

| X          | Y          | Z | F'(X,Y,Z)    |

| 0          | 0          | 0 |              |

| 0          | 0          | 1 |              |

| 0          | 1          | 0 |              |

| 0          | 1          | 1 |              |

| 1          | 0          | 0 |              |

| 1          | 0          | 1 |              |

| 1          | 1          | 0 |              |

| 1          | 1          | 1 |              |

Practice finding dual and complement functions/circuit realizations:

$\mathbf{F}(\mathbf{X},\mathbf{Y},\mathbf{Z}) = \mathbf{X} \bullet (\mathbf{Y} + \mathbf{Z}') + \mathbf{X}' \bullet \mathbf{Y}$

F<sup>D</sup>(X,Y,Z) the DUAL of function F, above

F'(X,Y,Z) the COMPLEMENT of function F, above

# In-Class Homework for Module 1 – No. 2 Friday, January 17, 2014

| 1. | Write a formula for OHM's LAW:                                                                                                                            |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Write a <u>formula</u> for POWER:                                                                                                                         |

| 3. | Describe what a <u>resistor</u> does:                                                                                                                     |

| 4. | Describe the <u>functionality</u> of a MOSFET:                                                                                                            |

| 5. | A <u>functional difference</u> between an N-channel MOSFET and a P-channel MOSFET is:                                                                     |

| 6. | Draw a symbol of a diode, label its terminals, and include the current arrow for a forward biased device.                                                 |

| 7. | Draw a symbol of a Light Emitting Diode with a current limiting resistor, label its terminals, and include the current arrow for a forward biased device. |

| • |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

# In-Class Homework for Module 1 – No. 3 Wednesday, January 22, 2014

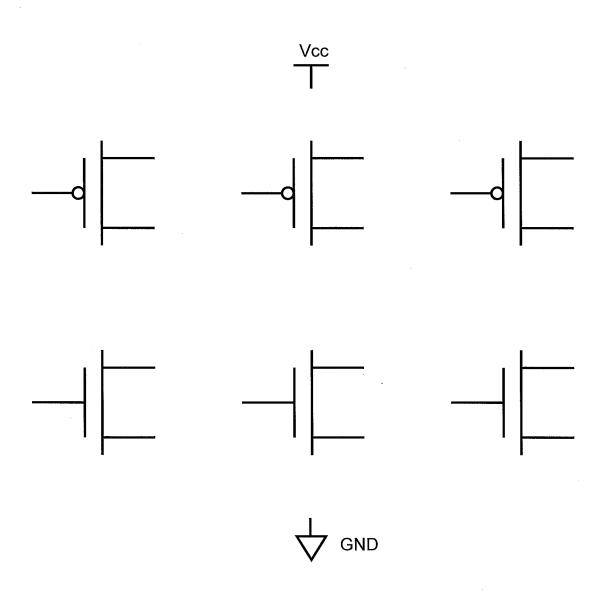

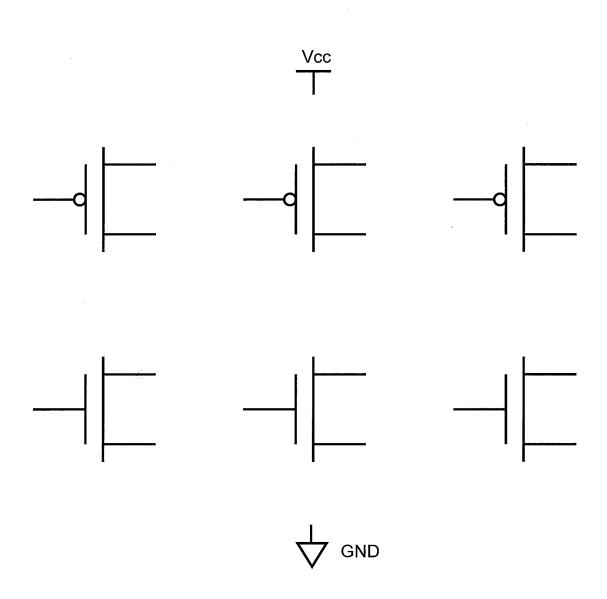

1. Using a total of **three** N-channel MOSFETs and **three** P-channel MOSFETs, draw a circuit schematic for a **two-input AND** gate. The gate inputs should be labeled A and B, and the gate output should be labeled F. Be sure to show the power (Vcc) and ground (GND) connections as well.

2. Using a total of **three** N-channel MOSFETs and **three** P-channel MOSFETs, draw a circuit schematic for a **three-input NOR** gate. The gate inputs should be labeled A, B, C and the gate output should be labeled F. Be sure to show the power (Vcc) and ground (GND) connections as well.

### In-Class Homework for Module 1 – No. 4 Monday, January 27, 2014

Assume two hypothetical logic families have the following D.C. characteristics:

### Logic Family "A"

| $V_{CC} = 5 \text{ V}$                     | $V_{OH} = 3.50 \text{ V}$ | $V_{\rm OL} = 0.50 \  m V$ | $V_{\rm IH} = 2.50 \ \rm V$ | $V_{\rm IL}$ = 1.00 V      |

|--------------------------------------------|---------------------------|----------------------------|-----------------------------|----------------------------|

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH} = -500 \mu A$     | $I_{OL} = 10 \text{ mA}$   | $I_{IH} = 50 \mu A$         | $I_{IL} = -1.5 \text{ mA}$ |

#### Logic Family "B"

| $V_{CC} = 5 \text{ V}$                     | $V_{OH} = 4.50 V$        | $V_{\rm OL} = 0.5 \ { m V}$ | $V_{IH} = 3.00 \text{ V}$ | $V_{\rm IL} = 1.50 \ { m V}$ |

|--------------------------------------------|--------------------------|-----------------------------|---------------------------|------------------------------|

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH} = -5 \text{ mA}$ | $I_{OL} = 10 \text{ mA}$    | $I_{IH} = 0.5 \mu A$      | $I_{\rm IL}$ = -0.5 $\mu A$  |

Can gates from family "B" be used to drive gates from family "A"? Explain your answer by calculating and considering fan-out and DC noise margin.

| $Fanout_{B\rightarrow A} = \underline{\hspace{1cm}}$     |  |  |  |

|----------------------------------------------------------|--|--|--|

| $\mathbf{DCNM}_{\mathbf{B}\to\mathbf{A}} = \underline{}$ |  |  |  |

| Conclusion:                                              |  |  |  |

Given that a (5-volt) CMOS gate's P-channel output pull-up has an "on" resistance of  $100\Omega$  and that its N-channel output pull-down has an "on" resistance of  $50\Omega$ :

| (a) | If the desired $V_{OHn}$ gate's $I_{OHmax}$ and $I_{OHmax}$ |                  | d the desired V <sub>OLmax</sub>                                                         | is 0.5 volts | s, what are the |

|-----|-------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------|--------------|-----------------|

|     | $I_{OHmax} = $                                              | mA               | $I_{ m OLmax} = $                                                                        | mA           |                 |

| (b) |                                                             |                  | for this CMOS gate face, based on the values                                             |              |                 |

|     |                                                             |                  |                                                                                          |              |                 |

|     | $\mathbf{V}_{\mathrm{IHmin}} = $                            | V                | $V_{ILmax} = $                                                                           | V            |                 |

| (c) |                                                             | is the practical | gates in this family and fan-out for circuits n part (a)?                                |              |                 |

|     | Practical fa                                                | n-out =          |                                                                                          |              |                 |

| (d) | gates in this family                                        | y to obtain max  | voltage $V_{LED} = 1.5 \text{ V}_{J}$<br>simum brightness, and red along with its power. | d calculat   | te the value of |

|     | Circuit and calcul                                          | ations:          |                                                                                          |              |                 |

|     |                                                             |                  |                                                                                          |              |                 |

|     |                                                             |                  |                                                                                          |              |                 |

|     |                                                             |                  |                                                                                          |              |                 |

Resistor power dissipation = \_\_\_\_ mW

Current limiting resistor =  $\Omega$

# In-Class Homework for Module 1 – No. 5 Wednesday, January 29, 2014

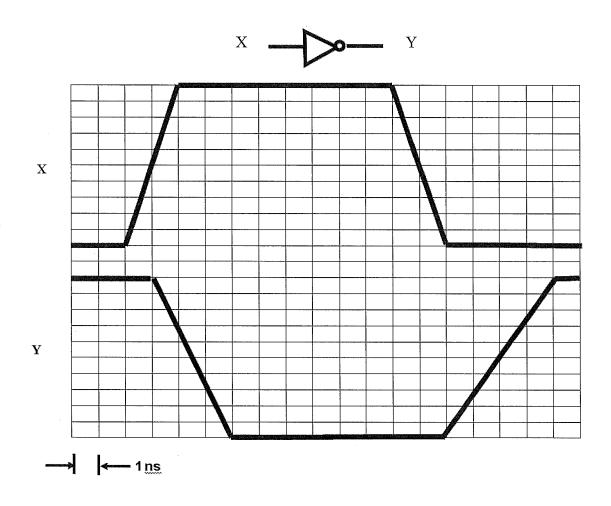

The timing diagram below depicts the input and output signals of an inverter. Determine the approximate  $t_{TLH}$ ,  $t_{THL}$ ,  $t_{PLH}$ , and  $t_{PHL}$  of the inverter.

The rise time  $(t_{TLH})$  for the inverter is approximately:

The fall time  $(t_{THL})$  for the inverter is approximately:

The fall propagation delay  $(t_{PHL})$  for the inverter is approximately:

The rise propagation delay  $(t_{PLH})$  for the inverter is approximately:

Given that a (5-volt) CMOS gate's P-channel output pull-up has an "on" resistance of  $100\Omega$  and that its N-channel output pull-down has an "on" resistance of  $50\Omega$ :

(a) If the desired  $I_{OH}$  and  $I_{OL}$  are 5 mA (i.e., -5 mA for  $I_{OH}$ , +5 mA for  $I_{OL}$ ), then the  $V_{OH}$  and  $V_{OL}$  specifications for this gate will be:

$V_{OH} =$

$V_{OL} = \underline{\hspace{1cm}}$

(b) If the  $V_{\text{IH}\text{min}}$  and  $V_{\text{IL}\text{max}}$  specifications are 3.5 volts and 1.5 volts, respectively, then the DCNM for this gate will be:

**DCNM** = \_\_\_\_\_

(c) If a gate from this family drives a capacitive load of 100 pF, estimate its rise and fall times.

Rise time estimate = ns

Fall time estimate = ns

### In-Class Homework for Module 1 – No. 6 Friday, January 31, 2014

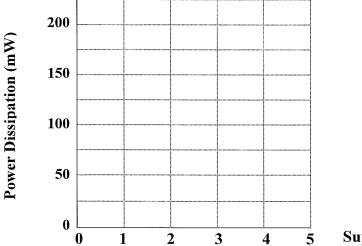

A particular CMOS microcontroller is design to operate over a supply voltage range of 2 V to 5 V and at a maximum clock frequency of 100 MHz (no minimum clock frequency is specified). The maximum power dissipation over this range of supply voltage and clock frequency is specified to be 200 milliwatts.

(a) Plot the relationship between power dissipation and supply voltage for this microcontroller.

Supply Voltage (V)

(b) Plot the relationship between *power dissipation* and *clock frequency* for this microcontroller.

Assume a CMOS microprocessor dissipates 100 milliwatts of power when operated at a clock frequency of 100 MHz with a supply voltage of 5 V. If the frequency of operation is reduced from 100 MHz to 40 MHz (and the supply voltage remains 5 V), the power dissipation will be reduced to:

Assume a CMOS microprocessor dissipates 100 milliwatts of power when operated at a clock frequency of 100 MHz with a supply voltage of 5 V. If the supply voltage is reduced from 5 V to 4 V (and the frequency of operation remains 100 MHz), the power dissipation will be reduced to:

Assume a CMOS microprocessor dissipates 100 milliwatts of power when operated at a clock frequency of 100 MHz with a supply voltage of 5 V. If the supply voltage is reduced from 5 V to 2 V and if the frequency of operation is reduced from 100 MHz to 50 MHz, the power dissipation will be reduced to:

#### In-Class Homework for Module 1 – No. 7 Monday, February 3, 2014

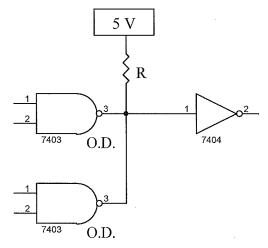

#### Given the following circuit:

(a) For the case of BOTH inputs of BOTH gates driven LOW: If the off-state leakage current of each of the 74x03 open-drain NAND gate outputs is  $+5~\mu A$ , and the  $I_{IH}$  required by the 74x04 inverter is  $+490~\mu A$ , determine the maximum value of R that will produce a  $V_{IH}$  of at least 4.5 volts at the 74x04 input.

Maximum R =

(b) For the case of both inputs of ONE gate driven HIGH and both inputs of the other gate driven LOW: If the  $I_{OLmax}$  of the 74x03 is specified to be +10 mA and that the  $I_{IL}$  required by the 74x04 inverter is -1 mA, determine the *minimum* value of R the will produce a  $V_{IL}$  of *no more than* 0.5 volts at the 74x04 input (assume the same off-state leakage current as Part (a), and round your answer to the nearest Ohm).

Minimum R =

(c) If you were guest starring on the hit TV series *Power of*  $1\theta_2$  and you were forced to choose one of these two values (i.e., the "Maximum R" or the "Minimum R"), which value would you choose, and why?

| Which value would you pick (circle one): | Minimum | -or- | Maximum |

|------------------------------------------|---------|------|---------|

| Why?                                     |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |

|                                          |         |      |         |