## Huddle Board Exercise for Module 4 – No. 1a Monday, April 14, 2014

Complete the following ABEL file so that it implements a 4-bit carry look-ahead adder based on the DECLARATIONS section provided below.

```

MODULE cla4

TITLE '4-bit Carry Look-Ahead Adder'

DECLARATIONS

X0..X3, Y0..Y3 pin; " operands

CIN pin; " carry in (Cin)

S0..S3 pin istype 'com'; " sum outputs

CO..C3 pin istype 'com'; " carry outputs (C3 is carry out)

PO..P3 pin istype 'com'; " propagate functions

G0 = X0&Y0; " generate functions

G1 = X1&Y1;

G2 = X2&Y2;

G3 = X3&Y3;

EQUATIONS

P0 = X0$Y0; " propagate functions

P1 = X1\$Y1;

P2 = X2$Y2;

P3 = X3$Y3;

" carry functions

C3 = ____

S0 = CIN$P0; " sum functions

S1 = C0\$P1;

S2 = C1\$P2;

S3 = C2$P3;

END

```

## Huddle Board Exercise for Module 4 – No. 1b Monday, April 14, 2014

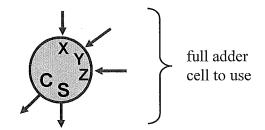

Draw a circuit that multiplies a 4-bit unsigned binary number X3 X2 X1 X0 by a 2-bit unsigned binary number Y1 Y0, using an array of full-adder cells. Determine the worst case propagation delay if each full adder takes 10 ns to produce its C and S outputs, and each AND gate (used to generate the product components) has 5 ns of propagation delay.

The worst case propagation delay is:

## Huddle Board Exercise for Module 4 – No. 2a Wednesday, April 16, 2014

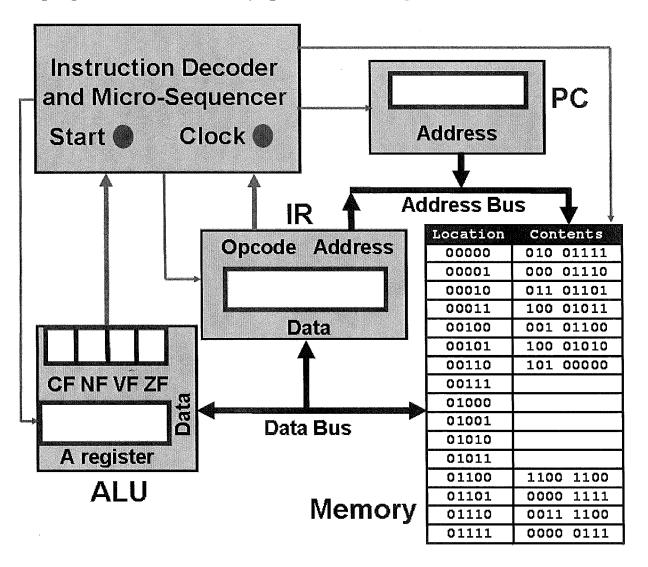

Assume the simple computer instruction set has been changed to the following:

| Opcode | Mnemonic | Function Performed                                  |

|--------|----------|-----------------------------------------------------|

| 0 0 0  | ADD addr | Add contents of <i>addr</i> to contents of A        |

| 0 0 1  | SUB addr | Subtract contents of <i>addr</i> from contents of A |

| 0 1 0  | LDA addr | Load A with contents of location addr               |

| 0 1 1  | XOR addr | XOR contents of <i>addr</i> with contents of A      |

| 100    | STA addr | Store contents of A at location <i>addr</i>         |

| 101    | HLT      | Halt – Stop, discontinue execution                  |

On the instruction trace worksheet, below, show the *final result* of executing the program stored in memory up to and including the HLT instruction.

## Huddle Board Exercise for Module 4 – No. 2b Wednesday, April 16, 2014

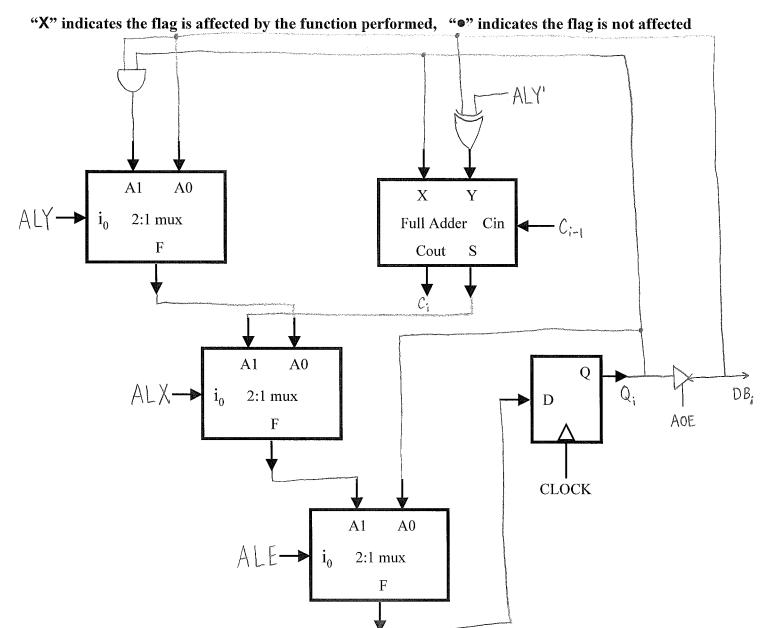

From the **BLOCK DIAGRAM** for one bit ("i") of the ALU, complete the table below:

| AOE | ALE | ALX | ALY | Function Performed                          | CF | ZF       | NF | VF |

|-----|-----|-----|-----|---------------------------------------------|----|----------|----|----|

|     |     |     |     | LDA: [Q3Q0] ← [D3D0]                        | •  | Х        | Х  | •  |

|     |     |     |     | AND: $[Q3Q0] \leftarrow [Q3Q0] \cap [D3D0]$ | •  | Х        | Х  | •  |

|     |     |     |     | SUB: [Q3Q0] ← [Q3Q0] – [D3D0]               | Х  | Х        | Х  | Х  |

|     |     |     |     | ADD: $[Q3Q0] \leftarrow [Q3Q0] + [D3D0]$    | Х  | Х        | Х  | Х  |

|     |     |     |     | OUT: [D3D0] ← [Q3Q0]                        | 0  | •        | •  | •  |

|     |     |     |     | (no operation – retain state)               |    | <b>Ø</b> |    | •  |