## Huddle Board Exercise for Module 1 – No. 1 Wednesday, January 22, 2014

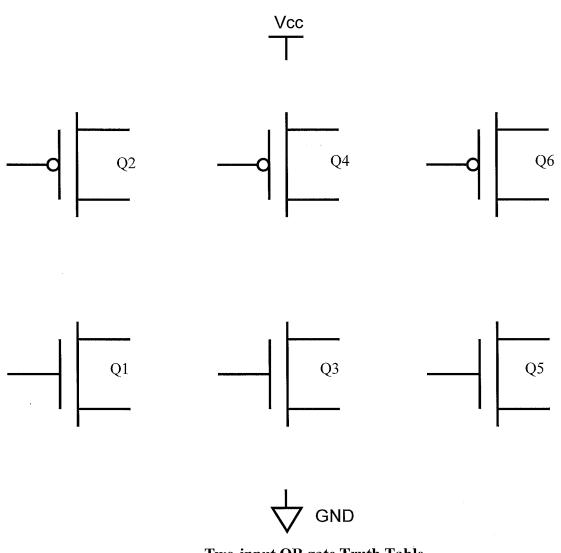

Draw a MOSFET-level circuit for a **2-input OR gate**. Label the inputs, A and B, and the output, F. The transistors, Q1, Q2, Q3, Q4, Q5, and Q6 are labeled. Be sure to include power (Vcc) and ground (GND) connections. In the truth table below, given the input values for A and B, determine if the transistor is "off" or "on" and the corresponding output.

**Two-input OR gate Truth Table**

| A | В | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | F |

|---|---|----|----|----|----|----|----|---|

| 0 | 0 |    |    |    |    |    |    |   |

| 0 | 1 |    |    |    |    |    |    |   |

| 1 | 0 |    |    |    |    |    |    |   |

| 1 | 1 |    |    |    |    |    |    |   |

| • |  |   |  |  |

|---|--|---|--|--|

|   |  | · |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

|   |  |   |  |  |

## Huddle Board Exercise for Module 1 – No. 1 Wednesday, January 22, 2014

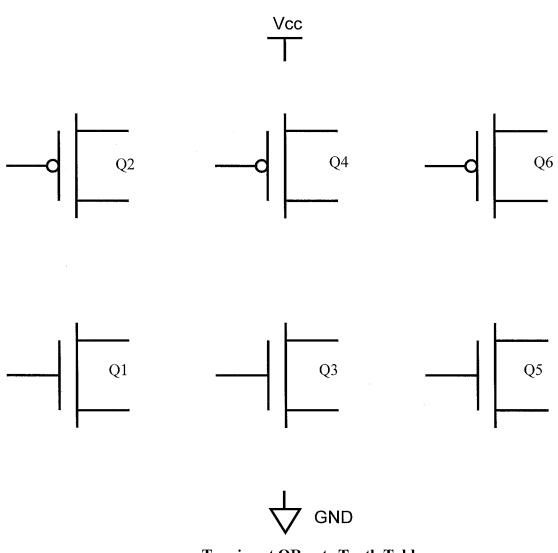

Draw a MOSFET-level circuit for a **2-input OR gate**. Label the inputs, A and B, and the output, F. The transistors, Q1, Q2, Q3, Q4, Q5, and Q6 are labeled. Be sure to include power (Vcc) and ground (GND) connections. In the truth table below, given the input values for A and B, determine if the transistor is "off" or "on" and the corresponding output.

Two-input OR gate Truth Table

| A | В | Q1  | Q2  | Q3  | Q4  | Q5  | Q6  | F |

|---|---|-----|-----|-----|-----|-----|-----|---|

| 0 | 0 | off | on  | off | on  | on  | off | 0 |

| 0 | 1 | off | on  | on  | off | off | on  | 1 |

| 1 | 0 | on  | off | off | on  | off | on  | 1 |

| 1 | 1 | on  | off | on  | off | off | on  | 1 |

|  |  | , |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

## Huddle Board Exercise for Module 1 – No. 2 Monday, January 27, 2014

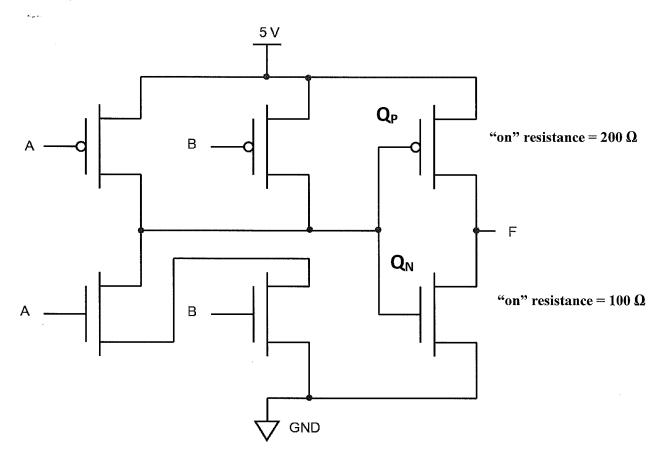

Use the following circuit to answer the questions below:

The circuit above represents this **type of gate:**

If the "on" resistance of the MOSFET labeled " $Q_P$ " is  $200\Omega$  and the "on" resistance of the MOSFET labeled " $Q_N$ " is  $100\Omega$ , then if 10mA of current is **sourced** in the high state,  $V_{OH}$  will be:

If the "on" resistance of the MOSFET labeled " $Q_P$ " is  $200\Omega$  and the "on" resistance of the MOSFET labeled " $Q_N$ " is  $100\Omega$ , then if 10mA of current is sunk in the low state,  $V_{OL}$  will be:

A common question students have relates to why the P-channel device has to serve as a "pull-up" while the N-channel device has to serve as a "pull-down" (i.e., why can't it be the "other way around"?). To convince yourself of this reality, try drawing a CMOS inverter "upside down" (with an N-channel device used as a pull-up and a P-channel device used as a pull-down) and analyze the circuit you have created (i.e., determine its Vi-Vo characteristics). Describe your conclusion.