#### Revisited Concept Exercise for Module 1 – No. 1 Wednesday, January 15, 2014

> Convert (3487)<sub>10</sub> to base 16

> Convert (C29E)<sub>16</sub> to base 2

> Convert (1101101)<sub>2</sub> to base 16

| ~ |   |

|---|---|

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   |   |

|   | , |

|   |   |

|   |   |

|   |   |

|   |   |

#### Revisited Concepts Exercise for Module 1 – No. 2a Friday, January 17, 2014

MATCHING – Write the letter of the example (on the right) corresponding to the named axiom or theorem:

| Involution     | A.        | $(\mathbf{X} \cdot \mathbf{Y}) \cdot \mathbf{Z} = \mathbf{X} \cdot (\mathbf{Y} \cdot \mathbf{Z})$                                                       |

|----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idempotency    | В.        | X+Y = Y+X                                                                                                                                               |

| Identity       | C.        | $\mathbf{X} \cdot \mathbf{Y} + \mathbf{X} \cdot \mathbf{Y'} = \mathbf{X}$                                                                               |

| Null Element   | D.        | $X \cdot X \cdot X = X$                                                                                                                                 |

| Complement     | <b>E.</b> | $X+(Y\cdot Z)=(X+Y)\cdot (X+Z)$                                                                                                                         |

| Associativity  | F.        | X + 1 = 1                                                                                                                                               |

| Commutivity    | G.        | $\mathbf{X} \cdot \mathbf{X}' = 0$                                                                                                                      |

| Distributivity | н.        | $(X+Y)' = X' \cdot Y'$                                                                                                                                  |

| Combining      | I.        | $(\mathbf{X}')' = \mathbf{X}$                                                                                                                           |

| DeMorgan's Law | J.        | $\mathbf{X} + 0 = \mathbf{X}$                                                                                                                           |

| Congengue      | K         | $\mathbf{X} \cdot \mathbf{V} + \mathbf{X}' \cdot \mathbf{Z} + \mathbf{V} \cdot \mathbf{Z} = \mathbf{X} \cdot \mathbf{V} + \mathbf{X}' \cdot \mathbf{Z}$ |

| · |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

#### Revisited Concepts Exercise for Module 1 – No. 2b Friday, January 17, 2014

MATCHING - Write the letter of the description (on the right) corresponding to the concept or device:

| Capacitor                         | A. | Difference in electrical potential                                                                                                                           |

|-----------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Computer                          | В. | The flow of charge in a conductor between two points having a difference in potential                                                                        |

| Current                           | С. | Amount of energy                                                                                                                                             |

| Forward Voltage                   | D. | A device that stores an electric charge                                                                                                                      |

| Integrated Circuit (IC or "Chip") | Е. | The voltage drop across a Light Emitting Diode when it is forward biased                                                                                     |

| Microcontroller                   | F. | A collection of logic gates and/or other electronic circuits fabricated on a single silicon chip                                                             |

| Microprocessor                    | G. | An integrated circuit onto which a generic logic circuit can be programmed                                                                                   |

| Power                             | Н. | A digital device that sequentially executes a stored program                                                                                                 |

| Programmable Logic Device (PLD)   | I. | A single-chip embodiment of the major functional blocks of a computer                                                                                        |

| Voltage                           | J. | A complete computer on a chip, including integrated peripherals                                                                                              |

| CMOS                              | K. | Fiberglass reinforced epoxy substrate with etched copper circuitry (typically in multiple layers) used to create virtually all electronic devices            |

| Discrete Logic                    | L. | A circuit constructed using small-scale<br>Integrated (SSI) and medium-scale integrated<br>(MSI) logic devices (NAND gates, decoders,<br>Multiplexers, etc.) |

| Printed Circuit Board (PCB)       | М. | A silicon chip fabrication technology based on<br>Use of complementary pairs of NMOS and<br>PMOS field effect transistors (MOSEFTs)                          |

## Revisited Concepts Exercise for Module 1 – No. 3 Wednesday, January 22, 2014

| 1. Describe the function of a P-channel MOSFET | LI. |

|------------------------------------------------|-----|

|------------------------------------------------|-----|

- 2. When a MOSFET is off, its drain-to-source impedance is on the order of:

- 3. Describe the <u>function</u> of a combinational circuit:

4. Fill out the truth table for a **NOT** gate:

Name of property:

| A | (A)' |

|---|------|

| 0 |      |

| 1 |      |

5. If I'm on a deserted island with my DK-1 kit (starring on the *Digital Survivor* show), I can build "anything digital" using only a bucket full of what (<u>single</u>) type of 2-input logic gate? What is the name of the property upon which this premise is based?

| Type of 2-input gate: | <br> |  |

|-----------------------|------|--|

|                       |      |  |

|                       |      |  |

|                       |      |  |

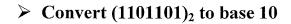

6. Using a total of **three** N-channel MOSFETs and **three** P-channel MOSFETs, draw a circuit schematic for a **three-input NAND** gate. The gate inputs should be labeled A, B, C and the gate output should be labeled F. Be sure to show the power (Vcc) and ground (GND) connections as well.

### Revisited Concepts Exercise for Module 1 - No. 4 Monday, January 27, 2014

1. Fill out the truth table for a **2-input NAND** gate:

| A | В | $(A \cdot B)'$ |

|---|---|----------------|

| 0 | 0 |                |

| 0 | 1 |                |

| 1 | 0 |                |

| 1 | 1 |                |

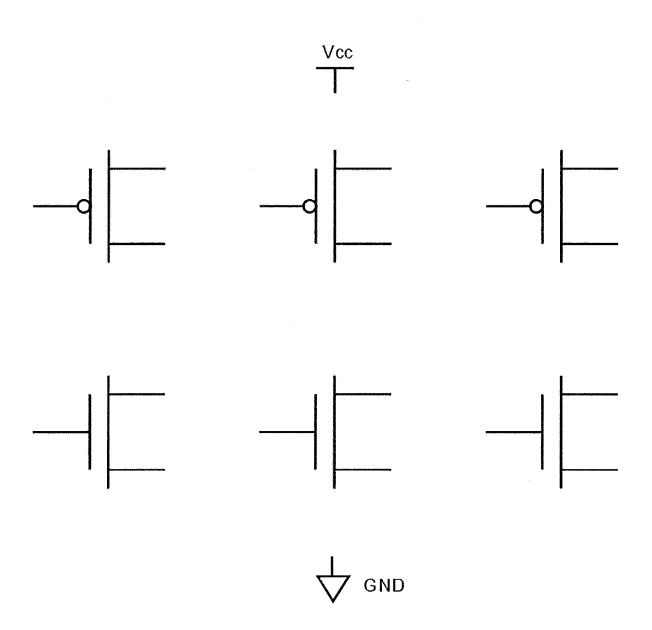

2. Draw a MOSFET-level circuit for a **2-input NAND** gate:

# Revisited Concepts Exercise for Module 1 – No. 5 Wednesday, January 29, 2014

| 1. | Is it possible to have a negative DCNM? If so, what would it mean?        |

|----|---------------------------------------------------------------------------|

| 2. | What is the minimum DCNM necessary to ensure a functional circuit?        |

| 3. | Is it possible to have a negative fan-out? If so, what would it mean?     |

| 4. | What is the minimum fan-out necessary to ensure a functional circuit?     |

| 5. | What is the factor that limits the practical fan-in of a CMOS logic gate? |

| • |  |

|---|--|

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

|   |  |

## Revisited Concepts Exercise for Module 1 – No. 6 Friday, January 31, 2014

Assume hypothetical logic family has the following D.C. characteristics:

| $V_{CC} = 5 \text{ V}$                     | $V_{OH} = 3.50 \text{ V}$  | $V_{\rm OL} = 0.50 \  m V$   | $V_{\rm IH} = 2.50~{ m V}$ | $V_{\rm IL} = 1.00 \ { m V}$ |

|--------------------------------------------|----------------------------|------------------------------|----------------------------|------------------------------|

| $V_{\rm TH} = (V_{\rm OH} - V_{\rm OL})/2$ | $I_{OH} = -5.0 \text{ mA}$ | $I_{\rm OL} = 10 \text{ mA}$ | $I_{IH} = 500 \mu A$       | $I_{\rm IL}$ = -2.0 mA       |

When interfacing an *LED* that has a *forward voltage* of 1.5 V to this logic family in a *current sourcing* configuration, *maximum brightness* will be achieved (within the rated specifications) using a current limiting resistor of the value along with its power dissipation:

| Circuit and calculations:    |                                 |

|------------------------------|---------------------------------|

|                              |                                 |

|                              |                                 |

|                              |                                 |

|                              |                                 |

|                              |                                 |

| Current limiting resistor =Ω | Resistor power dissipation = mW |

|                              |                                 |

When interfacing an LED that has a forward voltage of 1.5 V to this logic family in a current sinking configuration, maximum brightness will be achieved (within the rated specifications) using a current limiting resistor of the value along with its power dissipation:

| Circuit and calculations: |  |

|---------------------------|--|

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

|                           |  |

Current limiting resistor =  $_{ } \Omega$  Resistor power dissipation =  $_{ } mW$

#### Practice for standardized exam questions — determine the one best response.

- 1. When a gate's rated  $I_{OH}$  specification is exceeded, the following is likely to happen:

- (A) the  $V_{OH}$  of the gate will increase and the  $t_{TLH}$  of the gate will decrease

- (B) the  $V_{OH}$  of the gate will decrease and the  $t_{TLH}$  of the gate will increase

- (C) the  $V_{OL}$  of the gate will increase and the  $t_{THL}$  of the gate will increase

- (D) the  $V_{OL}$  of the gate will decrease and the  $t_{THL}$  of the gate will decrease

- (E) none of the above

- 2. When a gate's rated I<sub>OL</sub> specification is exceeded, the following is likely to happen:

- (A) the  $V_{OH}$  of the gate will increase and the  $t_{TLH}$  of the gate will decrease

- (B) the  $V_{OH}$  of the gate will decrease and the  $t_{TLH}$  of the gate will increase

- (C) the  $V_{OL}$  of the gate will increase and the  $t_{THL}$  of the gate will increase

- (D) the  $V_{OL}$  of the gate will decrease and the  $t_{THL}$  of the gate will decrease

- (E) none of the above

- 3. For CMOS gates,  $V_{\text{IHmin}}$  is typically:

- (A) 10% of the supply voltage (Vcc)

- (B) 30% of the supply voltage (Vcc)

- (C) 50% of the supply voltage (Vcc)

- (D) 70% of the supply voltage (Vcc)

- (E) 90% of the supply voltage (Vcc)

- 4. For CMOS gates, the *switching threshold* is typically:

- (A) 10% of the supply voltage (Vcc)

- (B) 30% of the supply voltage (Vcc)

- (C) 50% of the supply voltage (Vcc)

- (D) 70% of the supply voltage (Vcc)

- (E) 90% of the supply voltage (Vcc)

- 5. The largest source of noise in a digital circuit is from:

- (A) RF communication devices (e.g., cell phones)

- (B) cosmic rays

- (C) power line disturbances

- (D) the logic gates themselves

- (E) none of the above

- 6. Electromagnetic interference could cause a "floating" (unconnected) gate input to:

- (A) change from high-to-low or from low-to-high

- (B) increase the V<sub>IH</sub> of the gate relative to its specified value

- (C) decrease the  $V_{IL}$  of the gate relative to its specified value

- (D) pick up the satellite broadcast of a Purdue basketball victory

- (E) none of the above